- The Verilog-AMS Language

Ports, also referred to as pins or terminals, are used when wiring the module to other modules. As such, ports are wires. Ports declarations for simple wire are wire declarations with the keyword wire replaced by one of the following direction specifiers: input , output , or inout . For example:

For other types of wires, or for registers (registers may only be declared as outputs), the declaration is simply preceded by the direction specifier:

By default the content of multi-bit ports are interpreted as unsigned numbers (the values are interpreted as positive binary numbers). It is possible to explicitly specify whether the number is to be interpreted as a signed or unsigned number as follows:

In this case, gain is unsigned and offset is signed, which means it is interpreted as a twos-complement signed number. So, if gain = 4’bF, its value is interpreted as 15, and if offset = 7’b7FF, then its value is interpreted as -1.

If it is necessary to apply a discipline to a port, the port declaration should be repeated with direction specifier replaced by the discipline. For example:

Verilog also supports buses of continuous signals and wreals (you must declare these as buses rather than arrays):

The Cadence simulator does not seem to follow the standard when it comes to declaring buses of wreals. With the Cadence simulator you should declare buses of wreals as arrays rather than as buses:

Modules and Ports in Verilog

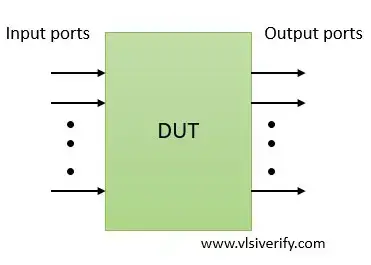

An interface to communicate with other modules or a testbench environment is called a port. In simple words, the input/ output pins of digital design are known as ports. This interface is termed a port interface or port list. Since the port list is available for connection, internal design implementation can be hidden from other modules or an environment.

|

|

|

Input port | input | To receive signal values from another module |

Output port | output | To send signal values to another module |

Bidirectional port | inout | To send or receive signal values to another module. |

Connection rules in Verilog port

While writing a module, the designer needs to make sure what type of signals have to be connected to the module’s inputs and outputs and follow the below rules.

|

|

|

|

input | reg or net | net | In an internal world, the input port must be of the net type and it can be connected to reg or net type variable in an external world. |

output | net | reg or net | In an internal world, the output port can be of reg or net type and it must be connected to the net type variable in an external world. |

inout | net | net | In an internal world, the inout port must be of the net type and it must be connected to the net type variable in an external world. |

Module instantiation

Method a: connecting a port list in an ordered manner.

An ordered manner connection is feasible when a port list has minimum signals as the user has to follow the same order in which design level signals are declared.

Method B: Connecting a port list by name

Assign Statement In Verilog

- You can use assign statement inside of module.

- You can use assign statement to output port and any wire declared inside the module

Examples of assign statement

In above example, y is output port and we are assigning this output port to a and b. It will create a and gate where a and b are inputs and y is output

In above example, we've descrived a NAND gate. We can use one statemetn but for better understanding we've use two statement to illustrate how we can use assign statement to both wire and output port. wire w is assign with a AND b, and output y is assigned not of wire w. This creates a NAND gate in verilog HDL.

In above example, we have described a full-adder using assign statement. Note that we can write complete boolean equation using assign statement

We can also use Verilog operators using assign statement. Below is the example of full-adder using assign statement and Verilog operator

In above example, we are using + operator, which addition operator in Verilog. We are assigning output sum and carry with addition of a, b and cin.

Click like if you found this useful

Add Comment

This policy contains information about your privacy. By posting, you are declaring that you understand this policy:

- Your name, rating, website address, town, country, state and comment will be publicly displayed if entered.

- Your IP address (not displayed)

- The time/date of your submission (displayed)

- Administrative purposes, should a need to contact you arise.

- To inform you of new comments, should you subscribe to receive notifications.

- A cookie may be set on your computer. This is used to remember your inputs. It will expire by itself.

This policy is subject to change at any time and without notice.

These terms and conditions contain rules about posting comments. By submitting a comment, you are declaring that you agree with these rules:

- Although the administrator will attempt to moderate comments, it is impossible for every comment to have been moderated at any given time.

- You acknowledge that all comments express the views and opinions of the original author and not those of the administrator.

- You agree not to post any material which is knowingly false, obscene, hateful, threatening, harassing or invasive of a person's privacy.

- The administrator has the right to edit, move or remove any comment for any reason and without notice.

Failure to comply with these rules may result in being banned from submitting further comments.

These terms and conditions are subject to change at any time and without notice.

Verilog Ports

In the previous article we covered how a block for a digital design can be defined in the Verilog using module … endmodule keywords. Let’s now move to the next part to see how we can define ports (inputs and outputs) in Verilog.

Verilog Ports Syntax

Verilog ports declaration provides the mechanism to define the signals as inputs and outputs. Syntax provided by the Verilog for ports declaration is as follows;

So for defining Verilog ports, we need four parameters which are as follows;

- Direction of the port

- Size of the port

- Type of the port

- Name of the port

Port Direction

Direction of the port defines whether the signal we intend to use as the port is the input to the module or going out of the module as the output. input and output keywords are used to define a signal as the input and output port respectively.

Port’s Data Type

Second field in port declaration is the data type of the port. Though Verilog provides a number of data types, only a few of them that are synthesizable and can be used for hardware design. Most commonly used data types are wire and reg type. reg is used for the signals for which we intend to store the data or their values are updated on the occurrence of some event thereby keeping the previous value retained for that length of time. While the wire type signals update their values instantly as soon as their input source changes its value.

The behaviour of this data type is almost similar to the wire used in actual hardwire in which we can store the current and it changes as soon as its input source changes its value. If we do not provide any data type for the port, it will by default be taken as wire .

Next part is the size of the port which defines how many bits of data will this port be carrying. The port size is defined using the square brackets [ ] e.g [ 7:0] . It means that the signal is a 8 bits port with bits from 7 down to 0. We can also define the port size in a more compact way using a number inside the square bracket. This number defines the size of the port in bits e.g [8] , it means that the signal is of 8 bits. So from the above discussion, [7:0] and [8] both define a port size of 8 bits. If you leave the size field blank, it defaults to 1 bit.

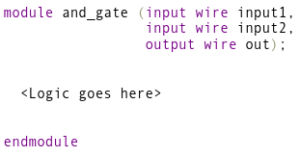

In the last part of the port declaration, we assign a name to the port. It is a recommended practice to have a meaningful name for the signal which depends upon its functionality. So continuing the example of AND design using Verilog, we can now define the ports for it. It has two 1-bit inputs and a 1-bit output. So now we have three signals on the port which are defined in terms of their fields as follows;

Table for AND gate Ports

| input | wire | input1 | ||

| input | wire | input2 | ||

| output | wire | out |

Here we can see that if we do not provide any size of the ports, it by default is 1 bit. Similarly the wire is the default data type. So now combining the port declaration with block or module definition, we get the external part of our digital design.

As we have covered the first two components of the digital design i.e block or module definition and ports declaration, from the next article we will move to the logic part and what features Verilog provide for logic building.

About The Author

I am the gold medalist from UET Lahore in electrical engineering and now I am working as the Manager and the Senior design Verification Engineer at 10xEngineers Lahore. I am also the founder of Nomaniyat which through its SemiRise training program is imparting technical skills to enable students and graduates to become part of the Semiconductor Industry. Till now approx 30 of our trainees have joined the industry. My major field of expertise include the design and verification of RISCV cores.

Leave a Reply Cancel reply

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

Verilog Assignments

Variable declaration assignment, net declaration assignment, assign deassign, force release.

- Procedural continuous

Legal LHS values

An assignment has two parts - right-hand side (RHS) and left-hand side (LHS) with an equal symbol (=) or a less than-equal symbol (<=) in between.

| Assignment type | Left-hand side |

|---|---|

| Procedural | |

| Continuous | |

| Procedural Continous |

The RHS can contain any expression that evaluates to a final value while the LHS indicates a net or a variable to which the value in RHS is being assigned.

Procedural Assignment

Procedural assignments occur within procedures such as always , initial , task and functions and are used to place values onto variables. The variable will hold the value until the next assignment to the same variable.

The value will be placed onto the variable when the simulation executes this statement at some point during simulation time. This can be controlled and modified the way we want by the use of control flow statements such as if-else-if , case statement and looping mechanisms.

An initial value can be placed onto a variable at the time of its declaration as shown next. The assignment does not have a duration and holds the value until the next assignment to the same variable happens. Note that variable declaration assignments to an array are not allowed.

If the variable is initialized during declaration and at time 0 in an initial block as shown below, the order of evaluation is not guaranteed, and hence can have either 8'h05 or 8'hee.

Procedural blocks and assignments will be covered in more detail in a later section.

Continuous Assignment

This is used to assign values onto scalar and vector nets and happens whenever there is a change in the RHS. It provides a way to model combinational logic without specifying an interconnection of gates and makes it easier to drive the net with logical expressions.

Whenever b or c changes its value, then the whole expression in RHS will be evaluated and a will be updated with the new value.

This allows us to place a continuous assignment on the same statement that declares the net. Note that because a net can be declared only once, only one declaration assignment is possible for a net.

Procedural Continuous Assignment

- assign ... deassign

- force ... release

This will override all procedural assignments to a variable and is deactivated by using the same signal with deassign . The value of the variable will remain same until the variable gets a new value through a procedural or procedural continuous assignment. The LHS of an assign statement cannot be a bit-select, part-select or an array reference but can be a variable or a concatenation of variables.

These are similar to the assign - deassign statements but can also be applied to nets and variables. The LHS can be a bit-select of a net, part-select of a net, variable or a net but cannot be the reference to an array and bit/part select of a variable. The force statment will override all other assignments made to the variable until it is released using the release keyword.

Stack Exchange Network

Stack Exchange network consists of 183 Q&A communities including Stack Overflow , the largest, most trusted online community for developers to learn, share their knowledge, and build their careers.

Q&A for work

Connect and share knowledge within a single location that is structured and easy to search.

What is supposed to happen in Verilog if a signal of one width is assigned to another signal of a different width?

As in these two cases:

What should A and D look like in terms of C and B respectively?

- \$\begingroup\$ it ought to spit at you both times, as you clearly don't know what you're doing. I've only ever been nice to it and assigned equal sized things. It might try and guess, or align LSB, I wait with bated breath for the answer. \$\endgroup\$ – Neil_UK Commented Jan 25, 2017 at 14:10

- \$\begingroup\$ Knowing this information is invaluable when debugging simulations. Obviously I don't intentionally code this way, but it'd be really convenient to know the convention so that I can recognize it when I accidentally have coded a mismatch. \$\endgroup\$ – user2600959 Commented Jan 25, 2017 at 14:15

Verilog's rules are:

- if you copy a narrower value into a wider target, it is zero-extended (zero MSBs added to the left), or sign-extended into the target. Whether it is zero or sign-extended is determined by the signedness of the right-hand-side expression.

- if you copy a wider value to a narrower target, it gets truncated (MSBs removed on the left).

So it means, in your case:

Note that most synthesis tools will issue a warning in these cases. And they should because it's then unclear you're doing things correctly.

- \$\begingroup\$ I was wondering this for simulation, as the simulator didn't issue warnings. If I had tried synthesis then I am sure it would have. Thank you for the help! \$\endgroup\$ – user2600959 Commented Jan 25, 2017 at 14:18

- \$\begingroup\$ Indeed, pure simulators may not show warnings, because they care more about pure Verilog's specifications than whether your code is meaningful. You'll see that synthesis tools may potentially leverage a lot of things that simulations tools don't. \$\endgroup\$ – dim Commented Jan 25, 2017 at 14:24

Your Answer

Sign up or log in, post as a guest.

Required, but never shown

By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .

Not the answer you're looking for? Browse other questions tagged verilog or ask your own question .

- The Overflow Blog

- At scale, anything that could fail definitely will

- Best practices for cost-efficient Kafka clusters

- Featured on Meta

- Announcing a change to the data-dump process

- Bringing clarity to status tag usage on meta sites

Hot Network Questions

- Can it be acceptable to take over CTRL + F shortcut in web app

- Does it make sense for the governments of my world to genetically engineer soldiers?

- In Lord Rosse's 1845 drawing of M51, was the galaxy depicted in white or black?

- What is the translation of a code monkey in French?

- "The earth was formless and void" Did the earth exist before God created the world?

- Why is the stall speed of an aircraft a specific speed?

- Not a cross, not a word (number crossword)

- Using rule-based symbology for overlapping layers in QGIS

- How to prevent my frozen dessert from going solid?

- quantulum abest, quo minus .

- Invest smaller lump sum vs investing (larger) monthly amount

- Why doesn’t dust interfere with the adhesion of geckos’ feet?

- Can the strength of evidence for a proposition P (e.g., P = "God exists") be assessed objectively?

- Asked to suggest referees 9 months after submission: what to do?

- How do I learn more about rocketry?

- Can I Use A Server In International Waters To Provide Illegal Content Without Getting Arrested?

- Can a quadrilateral polygon have 3 obtuse angles?

- Are all citizens of Saudi Arabia "considered Muslims by the state"?

- Movie from 80s or 90s about a helmet which allowed to detect non human people

- What should I do if my student has quarrel with my collaborator

- Can a British judge convict and sentence someone for contempt in their own court on the spot?

- What does "if you ever get up this way" mean?

- How to run only selected lines of a shell script?

- Why is there so much salt in cheese?

- Interview Q

Verilog Tutorial

| Port is an essential component of the Verilog module. Ports are used to communicate for a module with the external world through input and output. It communicates with the chip through its pins because of a module as a fabricated chip placed on a PCB. Every port in the port list must be declared as or . All ports declared as one of them is assumed to be wire by default to declare it, or else it is necessary to declare it again. Ports, also referred to as pins or terminals, are used when wiring the module to other modules. Each port in the port list is defined as input, output, or inout based on the port signal's direction. If a port declaration includes the net or variable types, then that port is considered completely declared. It is illegal to declare the same port in a net or variable type declaration. And if the port declaration does not include a net or variable type, then the port can be declared again in a net or variable type declaration. For example, consider the ports for top and full adder shown in the above image.

In , all port declarations are implicitly declared as . If a port is intended to be a wire, it is sufficient to declare it as output, input, or inout. Input and inout ports are generally declared as wires. However, if output ports hold their value, they must be declared as as shown below: and cannot be declared as reg.There are two methods of making connections between signals specified in the module instantiation and the ports in a module definition. It is the simple method for beginners. The signals to be connected must appear in the module instantiation in the same order as the ports in the module definition. For large designs where modules have approx 50 ports or above. In this situation, remembering the order of the ports in the module definition is complicated and impractical. Verilog provides the capability to connect external signals to ports by the port names, rather than by position. Another main reason for connecting ports by name is that as long as the port name is not changed, the order of ports in the port list of a module can be rearranged without changing the port connections in module instantiations. had the following way for port declaration.Here the module declaration had to first list of the names of ports within the brackets. And then the direction of those ports defined later within the body of the module. . It allowed the type to be specified inside the port list. |

- Send your Feedback to [email protected]

Help Others, Please Share

Learn Latest Tutorials

Transact-SQL

Reinforcement Learning

R Programming

React Native

Python Design Patterns

Python Pillow

Python Turtle

Preparation

Verbal Ability

Interview Questions

Company Questions

Trending Technologies

Artificial Intelligence

Cloud Computing

Data Science

Machine Learning

B.Tech / MCA

Data Structures

Operating System

Computer Network

Compiler Design

Computer Organization

Discrete Mathematics

Ethical Hacking

Computer Graphics

Software Engineering

Web Technology

Cyber Security

C Programming

Control System

Data Mining

Data Warehouse

Navigation Menu

Search code, repositories, users, issues, pull requests..., provide feedback.

We read every piece of feedback, and take your input very seriously.

Saved searches

Use saved searches to filter your results more quickly.

To see all available qualifiers, see our documentation .

- Notifications You must be signed in to change notification settings

therajnish143/Working-RAM-and-ROM-using-verilog

Folders and files.

| Name | Name | |||

|---|---|---|---|---|

| 6 Commits | ||||

Repository files navigation

Working-ram-and-rom-using-verilog, the single port ram.

The Dual Port RAM

Results and Discussions

Single-port ram module.

Inputs : ( data [7:0] 8-bit input data. addr [5:0] 6-bit address. en: Write enable signal. clk: Clock signal. ) Outputs: ( q [7:0]: 8-bit output data.) Behavior: ● Data is written to the RAM at the specified address on the rising clock edge if en is asserted. ● If en is not asserted, the address is stored in addr_reg . ● Output q is assigned the value from the RAM at the address stored in addr_reg . Simulation Flow: ● Generates a clock with a 10-time unit period. ● Applies test vectors at specific time points. ● Creates a VCD file for waveform simulation. ● Stops simulation after 90 time units. Simulation Results: ● The testbench aims to verify the correctness of the single-port RAM module by simulating various scenarios, including write and read operations. ● The waveform simulation results can be analyzed in the generated VCD file ( dump.vcd )

Dual-Port RAM Module

Inputs: (data_a [7:0] and data_b [7:0]: Input data for Port A and Port B. addr_a [5:0] and addr_b [5:0]`: Address for Port A and Port B.

en_a and en_b : Write enable for Port A and Port B. clk : Clock signal ) **Outputs: **(q_a [7:0] and q_b [7:0]: Output data at Port A and Port B.) Behavior: ● On the rising edge of the clock ( posedge clk ): ● If en_a is asserted, write data_a to the RAM at address addr_a . ● If en_a is not asserted, assign q_a the value from the RAM at address addr_a . ● Similarly for Port B ( en_b , data_b , addr_b , and q_b ). Testbench Inputs : (data_a [7:0] and data_b [7:0]: Testbench input data. addr_a [5:0] and addr_b [5:0]: Testbench address for Port A and Port B. we_a and we_b: Testbench write enable for Port A and Port B. clk: Testbench clock.) Testbench Outputs: ( q_a [7:0] and q_b [7:0]: Testbench output data at Port A and Port B.) Testbench Simulation Flow: ● Set initial values for inputs (data_a, addr_a, we_a, data_b, addr_b, we_b). ● Apply test vectors at specific time points. ● Stop the simulation after 40 time units. Test Vector Details: ● Write data to Port A and Port B at different addresses with write enable control. ● Modify and read data from different addresses for Port A and Port B

Inputs: (clk: Clock signal, en: Enable signal , addr [3:0] : 4-bit address.) Outputs: (q [3:0] : 4-bit output data. ) Behavior: ● On the rising edge of the clock ( posedge clk ), if en is asserted, output q is assigned the value from memory at the specified address ( addr ). ● If en is not asserted, output q is set to an undefined value ( 4'bxxxx ). Initial Block: - Initializes the memory with specific 4-bit values at 16 different locations. Testbench Inputs: ( clk : Testbench clock. - en : Testbench enable. - addr [3:0] : Testbench address.) Testbench Outputs: - ( data [3:0] : Testbench output data.) Testbench Initial Blocks: ● $dumpfile and $dumpvars are used to create a VCD file for waveform simulation. - A clock ( clk`) is generated with a period of 10 time units.

● Test vectors are applied to the ROM inputs ( en , addr ) at specific time points. ● The simulation is stopped after 80 time units using $stop . Testbench Simulation Flow: ● Set initial values for inputs ( en , addr ). ● Apply test vectors at specific time points. ● Stop the simulation after 80 time units. Test Vector Details: ● Enable ( en ) and disable ( en=0 ) ROM output at specific addresses. - Change the address ( addr ) to observe different data outputs. ● Set an undefined address ( addr = 4'bxxxx ) to observe an undefined output. Simulation Results: ● The testbench aims to verify the correctness of the ROM module by simulating various scenarios, including enabling/disabling output and reading data from different addresses. ● The waveform simulation results can be analyzed in the generated VCD file ( dump.vcd ).

- Verilog 100.0%

- Stack Overflow for Teams Where developers & technologists share private knowledge with coworkers

- Advertising & Talent Reach devs & technologists worldwide about your product, service or employer brand

- OverflowAI GenAI features for Teams

- OverflowAPI Train & fine-tune LLMs

- Labs The future of collective knowledge sharing

- About the company Visit the blog

Collectives™ on Stack Overflow

Find centralized, trusted content and collaborate around the technologies you use most.

Q&A for work

Connect and share knowledge within a single location that is structured and easy to search.

Get early access and see previews of new features.

Output port continuous assignment problem

I have the code below, which is an array of shift registers connected to each other.

i.e., Sin->sr1->sr2->...sr14->sr15->sr16->Sout.

I got some errors (below) when trying to compile. I have declared the ports as wires, but I still have the same problem. Could you help solve the errors as I can't seem to see the issue?

You declared the signal as:

When you plug in the parameter values, this resolves to:

This is an array of 4 elements (0 to 3), each of which is 4 bits wide.

The problem is this line inside the for loops:

When i is set to its maximum value of 3 in the loop, i+1 is 4, which resolves to:

But, there is no shift_reg[4] element of the array. That explains the warning message. You are selecting an element which is not in the array ("out of bounds").

I don't understand the error message, but I suspect it will go away if you fix the code that produces the warning.

- yes, thanks, I tried [i] instead of [i+1] and it went without errors/warnings. The warning should have been the error :) – temp1445 Commented Oct 30, 2022 at 11:13

Your Answer

Reminder: Answers generated by artificial intelligence tools are not allowed on Stack Overflow. Learn more

Sign up or log in

Post as a guest.

Required, but never shown

By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .

Not the answer you're looking for? Browse other questions tagged verilog or ask your own question .

- The Overflow Blog

- At scale, anything that could fail definitely will

- Best practices for cost-efficient Kafka clusters

- Featured on Meta

- Announcing a change to the data-dump process

- Bringing clarity to status tag usage on meta sites

- What does a new user need in a homepage experience on Stack Overflow?

- Feedback requested: How do you use tag hover descriptions for curating and do...

- Staging Ground Reviewer Motivation

Hot Network Questions

- How best to cut (slightly) varying size notches in long piece of trim

- Multiple alien species on Earth at the same time: one species destroys Earth but the other preserves a small group of humans

- Could an empire rise by economic power?

- Is it possible to travel to USA with legal cannabis?

- Can Christian Saudi Nationals Visit Mecca?

- Is it possible to draw a series of mutually perpendicular curves in TikZ?

- Why am I having problems starting my service in Red Hat Enterprise Linux 8?

- Is there a simple way to fully change user id name in Windows 11 so it doesn't contain a space in it?

- What rules of legal ethics apply to information a lawyer learns during a consultation?

- How to run only selected lines of a shell script?

- Escape from the magic prison

- Nearly stalled on takeoff after just 3 hours training on a PPL. Is this normal?

- Why do the opposite of skillful virtues result in remorse?

- Largest number possible with +, -, ÷

- How would humans actually colonize mars?

- Geometry nodes: Curve caps horizontal

- If a Palestinian converts to Judaism, can they get Israeli citizenship?

- Can Christian Saudi Nationals visit Mecca?

- Can I Use A Server In International Waters To Provide Illegal Content Without Getting Arrested?

- How to resolve this calculation prompt that appears after running the drawing program?

- How can coordinates be meaningless in General Relativity?

- How do I safely download and run an older version of software for testing without interfering with the currently installed version?

- Convert 8 Bit brainfuck to 1 bit Brainfuck / Boolfuck

- Is it possible to recover from a graveyard spiral?

IMAGES

VIDEO

COMMENTS

Verilog 2001 onwards. Ports are a set of signals that act as inputs and outputs to a particular module and are the primary way of communicating with it. Think of a module as a fabricated chip placed on a PCB and it becomes quite obvious that the only way to communicate with the chip is through its pins. Ports are like pins and are used by the ...

If you must use any port as inout, Here are few things to remember: You can't read and write inout port simultaneously, hence kept highZ for reading. inout port can NEVER be of type reg. There should be a condition at which it should be written. (data in mem should be written when Write = 1 and should be able to read when Write = 0). For e.g.

3. In Verilog, you can only do a constant assignment to a type. A type is used in an block to assign something based on a sensitivity list (it can be synchronous, e.g. flip-flop, or asynchronous, e.g. latch, or gate). A type is used for assignments using the keyword or when connecting ports. When you connect something to a port using the ...

According to my knowledge (if it is correct), we can either declare a single wire (let its name be connection) and replace both <connection1> and <connection2> with it, or we can declare two distinct wires connection1 and connection2, then: assign connection2 = connection1; And connect them accordingly.

Ports, also referred to as pins or terminals, are used when wiring the module to other modules. As such, ports are wires. Ports declarations for simple wire are wire declarations with the keyword wire replaced by one of the following direction specifiers: input, output, or inout. For example: output out; input in;

Verilog assign statement. Signals of type wire or a similar wire like data type requires the continuous assignment of a value. For example, consider an electrical wire used to connect pieces on a breadboard. As long as the +5V battery is applied to one end of the wire, the component connected to the other end of the wire will get the required ...

A Module is a basic building design block in Verilog and it can be an element that implements necessary functionality. It can also be a collection of lower-level design blocks. As a part of defining a module, it has a module name, port interface, and parameters (optional). The port interface i.e. inputs and outputs is used to connect the high ...

Assign Statement In Verilog. assign keyword is used to assign ouput port or wire some digital logic. This keyword is the part of dataflow modeling in Verilog. In this post, we will see how to use this keyword in your Verilog code. You can use assign statement inside of module. You can use assign statement to output port and any wire declared ...

Port Name. In the last part of the port declaration, we assign a name to the port. It is a recommended practice to have a meaningful name for the signal which depends upon its functionality. So continuing the example of AND design using Verilog, we can now define the ports for it. It has two 1-bit inputs and a 1-bit output.

Verilog Module Instantiations. Port Connection by ordered list. Port Connection by name. Unconnected/Floating Ports. Example. As we saw in a previous article , bigger and complex designs are built by integrating multiple modules in a hierarchical manner. Modules can be instantiated within other modules and ports of these instances can be ...

assign y = ce ? d : q; endmodule Example 1 - Verilog-1995 version of the muxff module A Verilog-1995 version of this model requires that the q-port be declared three times: once in the module header, once as an output port and once as a reg-variable data type. The d, clk, ce and rst_n ports must all be declared twice: once in the module header ...

there is no way in verilog to declare different directions to different bits of a single vector port. The direction works on the whole declaration of a port. The only way to do it is to split the single port into multiple ports with different names, e.g. module main( output wire tx, input wire rx, output wire out, input wire in );

port connections, and (4) using new SystemVerilog .* implicit port connections. The styles are compared for coding effort and efficiency. 2.1 Verilog positional port connections Verilog has always permitted positional port connections. The Verilog code for the positional port connections for the CALU block diagram is shown in Example 1.

Assignments Appendix (UniversityofMichigan) Lab1: Verilog August30,20242/68. EECS470 Help? ContactInformation ... (UniversityofMichigan) Lab1: Verilog August30,20244/68. EECS470 What? Lab1-VerilogIntroduction Lab2-TheBuildSystem Lab3-WritingGoodTestbenches Lab4-Scripting Lab5-SystemVerilog

Hi All, I have a port of an interface, which I would like to force to a value for all instances of interface. Do we have an efficient way to implement this, rather than adding force for each interface's instance. ... Edit, save, simulate, synthesize SystemVerilog, Verilog, VHDL and other HDLs from your web browser. tsowmya August 1, 2020, 2 ...

Although it is Cliff's proposal to remove Type Reg, as part of that, he explains Verilog types in detail in this paper. This paper will detail the differences between register and net data types and propose an enhancement to the Verilog language that would eliminate the need to declare register data types altogether

The LHS of an assign statement cannot be a bit-select, part-select or an array reference but can be a variable or a concatenation of variables. reg q; initial begin assign q = 0; #10 deassign q; end force release. These are similar to the assign - deassign statements but can also be applied to nets and variables. The LHS can be a bit-select of ...

Verilog's rules are: if you copy a narrower value into a wider target, it is zero-extended (zero MSBs added to the left), or sign-extended into the target. Whether it is zero or sign-extended is determined by the signedness of the right-hand-side expression.

Verilog Ports. Port is an essential component of the Verilog module. Ports are used to communicate for a module with the external world through input and output. It communicates with the chip through its pins because of a module as a fabricated chip placed on a PCB. Every port in the port list must be declared as input, output or inout.

You've declared digit_1/2 as a variable and it needs to be a net in Verilog I'm assuming those are output ports from your binary_bcd_2 module. SystemVerilog does not have this restriction. Simply remove the reg keyword from the port declaration. I've added wire for clarity, but that is what is implicit

Inputs: ( data [7:0] 8-bit input data. addr [5:0] 6-bit address. en: Write enable signal. clk: Clock signal. Outputs:( q [7:0]: 8-bit output data.) Behavior: Data is written to the RAM at the specified address on the rising clock edge if en is asserted. If en is not asserted, the address is stored in addr_reg. Output q is assigned the value from the RAM at the address stored in addr_reg.

Verilog inout port assignment results in X Hot Network Questions Replacing aircon capacitor, using off brand same spec vs lower/higher spec from correct brand?